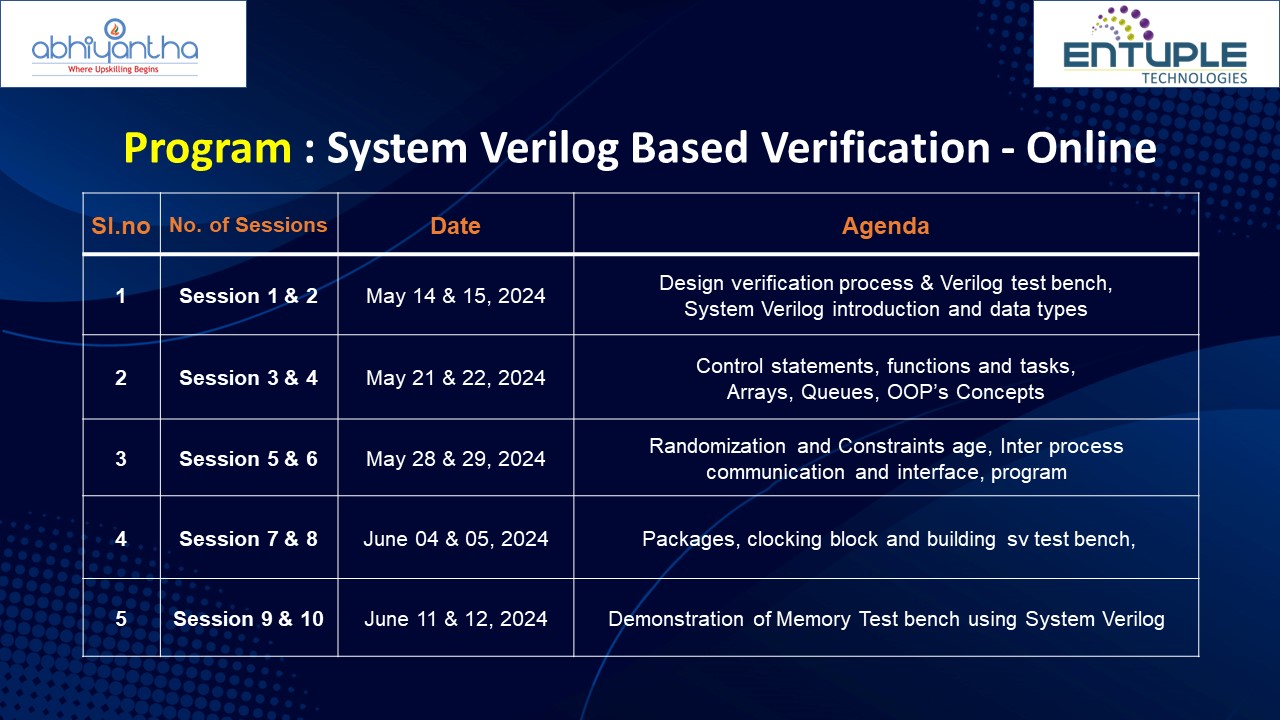

System Verilog Based Verification

Start Date : 14 May'2024 |

Timings: 6:30 PM to 8:30 PM |

Mode : Online (Tuesday - wednesday) |

Duration : 6 weeks

Course Fee

₹12,999 ₹3,999 + GST

- Live Interactive Sessions

- Assignment & Quizzes

- LMS Access - revisit concepts

- Technical Support

- Certificate of Completion

- 20 hours of Cadence EDA Tool Access*

- *Note : Nominal fee applies (Optional).

Course Includes

- Verilog HDL.

- Basic Digital Design.

Prerequisites

- Students, Faculties, Technical Staffs, Working Professional.

- Core Engineers, Explore career alternatives prior to graduation.

Who can Benefit